## Hardware Reference Manual

REV. August 2018

## **Blackbird**

(VL-EPU-4562/4462)

Intel® Core™-based Embedded Processing Unit with SATA, Dual Ethernet, USB, Digital I/O, Serial, Video, Mini PCle Sockets, SPX, Trusted Platform Module

### WWW.VERSALOGIC.COM

12100 SW Tualatin Road Tualatin, OR 97062-7341 (503) 747-2261 Fax (971) 224-4708

Copyright © 2017-2018 VersaLogic Corp. All rights reserved.

### Notice:

Although every effort has been made to ensure this document is error-free, VersaLogic makes no representations or warranties with respect to this product and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose.

VersaLogic reserves the right to revise this product and associated documentation at any time without obligation to notify anyone of such changes.

\* Other names and brands may be claimed as the property of others.

#### **Product Revision Notes**

| Revision 1.00                                       | Initial release                                    |

|-----------------------------------------------------|----------------------------------------------------|

| Revision 1.01                                       | Replaced block diagram                             |

| Revision 1.02 Updated Web links and WDT information |                                                    |

| Revision 1.03                                       | Updated Power Connector Pinout diagram (Figure 7)  |

| Revision 1.04                                       | Replaced Power Connector Pinout diagram (Figure 7) |

## **Support Page**

The <u>Blackbird Support Page</u> contains additional information and resources for this product including:

- Operating system information and software drivers

- Data sheets and manufacturers links for chips used in this product

- BIOS information and upgrades

## VersaTech KnowledgeBase

The <u>VersaTech KnowledgeBase</u> contains useful technical information about VersaLogic products, along with product advisories.

## **Customer Support**

If you are unable to solve a problem after reading this manual, visiting the product support page, or searching the KnowledgeBase, contact VersaLogic Technical Support at (503) 747-2261. VersaLogic support engineers are also available via e-mail at Support@VersaLogic.com.

## **Repair Service**

If your product requires service, you must obtain a Returned Material Authorization (RMA) number by calling 503-747-2261. Be ready to provide the following information:

- Your name, the name of your company, your phone number, and e-mail address

- The name of a technician or engineer that can be contacted if any questions arise

- The quantity of items being returned

- The model and serial number (barcode) of each item

- A detailed description of the problem

- Steps you have taken to resolve or recreate the problem

- The return shipping address

Warranty Repair All parts and labor charges are covered, including return shipping

charges for UPS Ground delivery to United States addresses.

**Non-warranty Repair** All approved non-warranty repairs are subject to diagnosis and labor

charges, parts charges and return shipping fees. Specify the shipping method you prefer and provide a purchase order number for invoicing

the repair.

**Note:** Mark the RMA number clearly on the outside of the box before returning.

## **Cautions**

## **Electrostatic Discharge**

#### **CAUTION:**

Electrostatic discharge (ESD) can damage circuit boards, disk drives, and other components. The circuit board must only be handled at an ESD workstation. If an approved station is not available, some measure of protection can be provided by wearing a grounded antistatic wrist strap. Keep all plastic away from the board, and do not slide the board over any surface.

After removing the board from its protective wrapper, place the board on a grounded, static-free surface, component side up. Use an antistatic foam pad if available.

The board should also be protected inside a closed metallic antistatic envelope during shipment or storage.

**Note:** The exterior coating on some metallic antistatic bags is sufficiently conductive to cause excessive battery drain if the bag comes in contact with the bottom side of the Blackbird.

## **Handling Care**

#### **CAUTION:**

Avoid touching the exposed circuitry with your fingers when handling the board. Though it will not damage the circuitry, it is possible that small amounts of oil or perspiration on the skin could have enough conductivity to cause the contents of CMOS RAM to become corrupted through careless handling, resulting in CMOS resetting to factory defaults.

#### **Earth Ground Requirement**

#### **CAUTION:**

All mounting standoffs should be connected to earth ground (chassis ground). This provides proper grounding for EMI purposes.

## **Contents**

| Cautions                        | iv |

|---------------------------------|----|

| Electrostatic Discharge         | iv |

| Handling Care                   | iv |

| Earth Ground Requirement        | iv |

| Introduction                    | 9  |

| Features                        |    |

| Technical Specifications        |    |

| Block Diagram                   |    |

| Dimensions and Mounting         |    |

| Blackbird Dimensions            |    |

| Configuration and Setup         | 13 |

| Initial Configuration           |    |

| Basic Setup                     |    |

| BIOS Setup Utility              |    |

| Default BIOS Setup Values       |    |

| Operating System Installation.  |    |

| Jumper Blocks                   |    |

| Jumper As-Shipped Configuration |    |

| Jumper Configuration Summary    |    |

| Board Features                  | 18 |

| CPU                             |    |

| CPU Die Temperature             |    |

| System RAM                      |    |

| I/O Interfaces                  |    |

| Real-Time Clock (RTC)           |    |

| External Connectors             |    |

| Baseboard Connector Locations   |    |

| Power Delivery                  |    |

| Main Power Connector            |    |

| Cabling                         |    |

| Power Requirements              |    |

| Power Delivery Considerations   |    |

| Power Button                    |    |

| Supported Power States          |    |

| Battery Power Options           |    |

| External Speaker                |    |

| Push-button Reset               |    |

| CPU Fan Connector               |    |

| Cabling                         |    |

| LEDs                            |    |

| Power-Good/Fault Indicator LEDs |    |

| Mass Storage Interfaces         | 31 |

| SATA Interface                                                | 31 |

|---------------------------------------------------------------|----|

| Multi-purpose I/O                                             | 33 |

| USB Interfaces                                                |    |

| Mini PCIe Sockets                                             | 34 |

| W DISABLE# Signal                                             | 36 |

| Mini PCIe Card Status LEDs                                    | 37 |

| User I/O Connector                                            | 38 |

| Cabling                                                       |    |

| Analog-to-Digital and Digital to Analog Converter Interface   |    |

| Cabling                                                       |    |

| SPX <sup>TM</sup> Expansion Bus                               |    |

| Cabling                                                       |    |

| Serial I/O                                                    | 44 |

| Serial Ports                                                  | 44 |

| Serial Port Connector Pinout                                  | 45 |

| Cabling                                                       | 45 |

| COM Port Configuration                                        |    |

| Console Redirection                                           | 46 |

| Video Interfaces                                              | 47 |

| Mini DisplayPort++ (DP++) Connectors                          | 47 |

| VGA Output                                                    | 49 |

| LVDS Interface                                                | 50 |

| LVDS Flat Panel Display Connector                             | 50 |

| LVDS Backlight Connector                                      |    |

| Network Interfaces                                            | 53 |

| Ethernet Connector                                            | 53 |

| Cabling                                                       | 54 |

| Ethernet Status LEDs                                          |    |

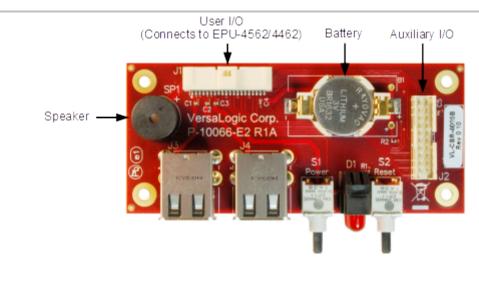

| VL-CBR-4005B Paddleboard                                      | 56 |

| VL-CBR-4005B Connectors and Indicators                        | 56 |

| User I/O Connector                                            | 57 |

| Cabling                                                       | 58 |

| On-board Battery                                              | 58 |

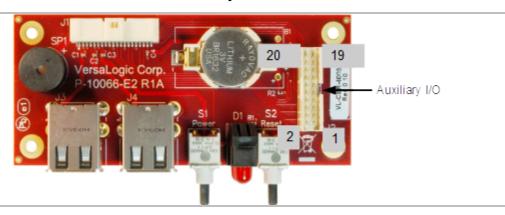

| Auxiliary I/O Connector                                       |    |

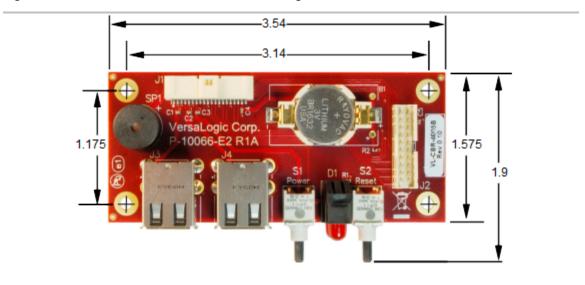

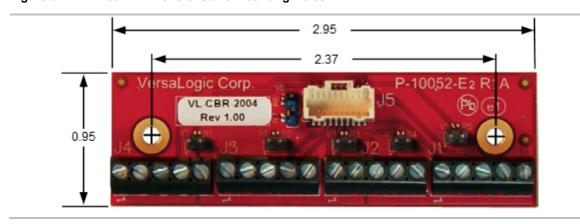

| Dimensions and Mounting Holes                                 | 60 |

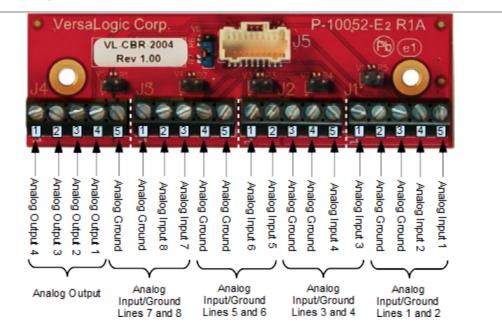

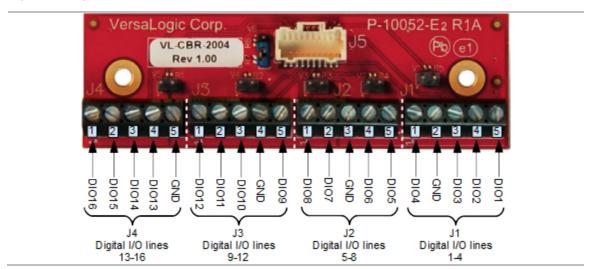

| Digital and Analog I/O Paddleboards                           | 61 |

| Analog I/O (Using VL-CBR-2004)                                | 61 |

| Digital I/O (Using VL-CBR-2005)                               | 62 |

| Dimensions and Mounting Holes                                 | 63 |

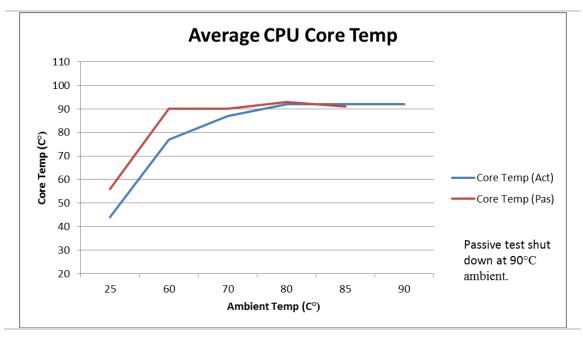

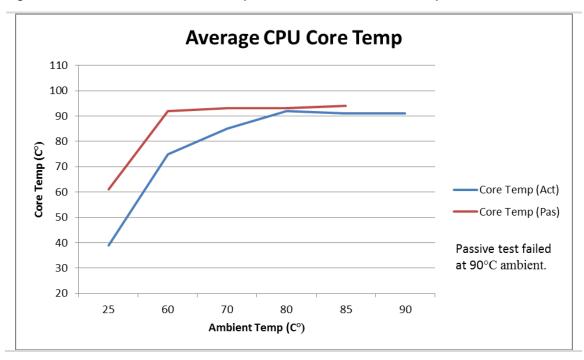

| Thermal Considerations                                        | 64 |

| Selecting the Correct Thermal Solution for Your Application . | 64 |

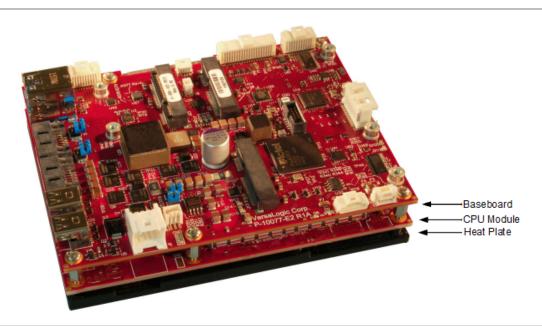

| Heat Plate                                                    |    |

| System-level Considerations                                   | 64 |

| CPU Thermal Trip Points                                       |    |

| Thermal Specifications, Restrictions, and Conditions.         |    |

| Overall Restrictions and Conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 67      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Heat Plate Only Restrictions and Conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67      |

| Heat Sink Only Considerations:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| Heat Sink with Fan Considerations:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |

| EPU-4562/4462 Thermal Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

| Test Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

| Hardware Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

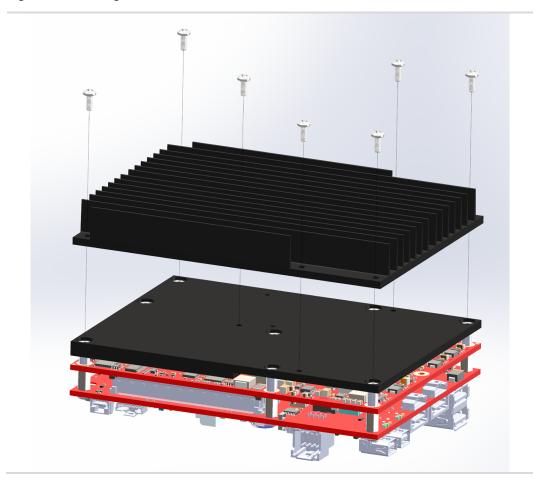

| Installing the VL-HDW-417 Passive Heat Sink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |

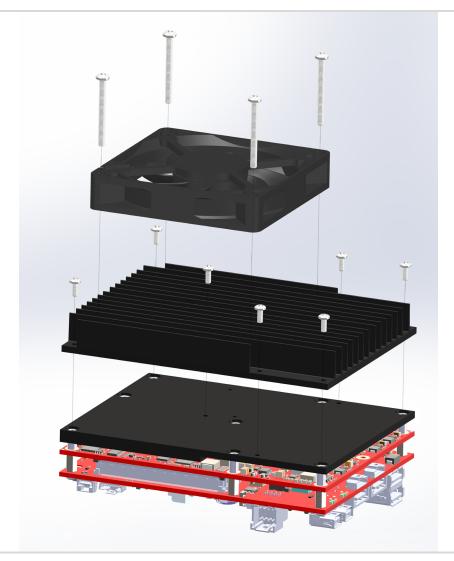

| Installing the VL-HDW-418 Heat Sink Fan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |

| KNOWN ISSUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 74      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figures |

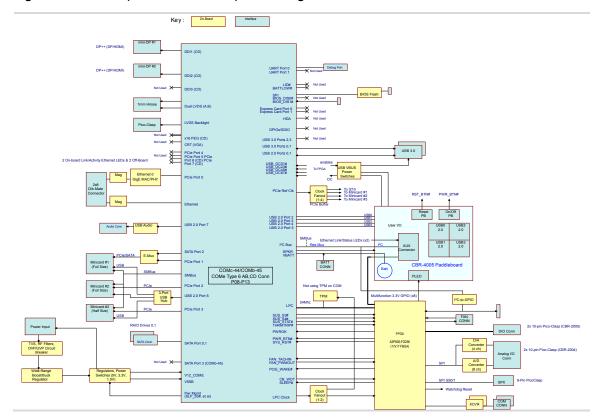

| Figure 1. Blookkind (VI. EDIJ 4562/4462) Blook Diogram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11      |

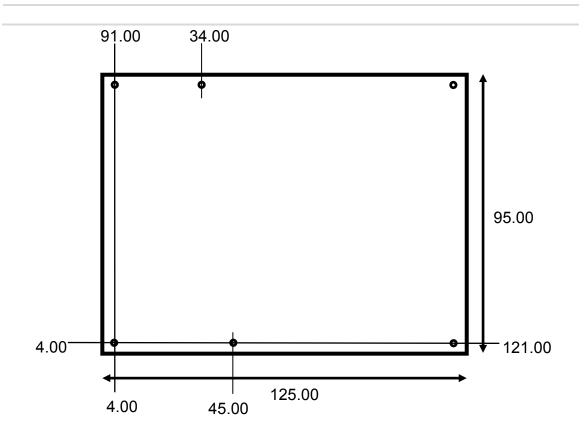

| Figure 1. Blackbird (VL-EPU-4562/4462) Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

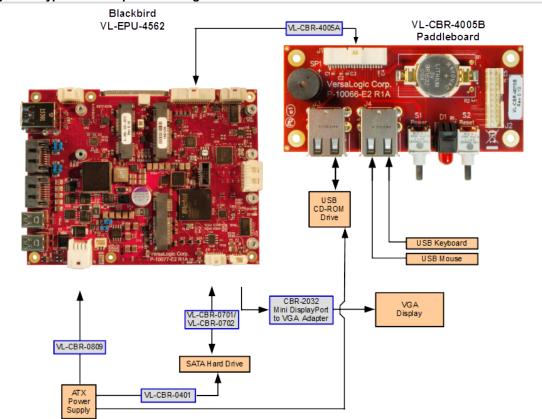

| Figure 3. Typical Development Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |

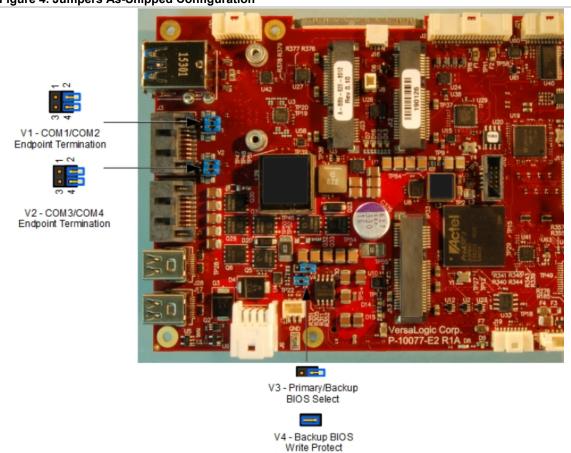

| Figure 4. Jumpers As-Shipped Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |

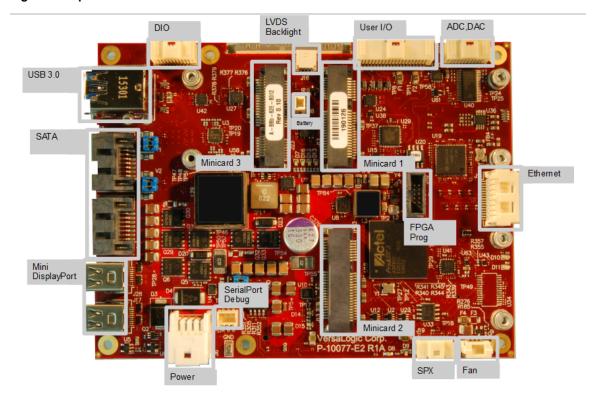

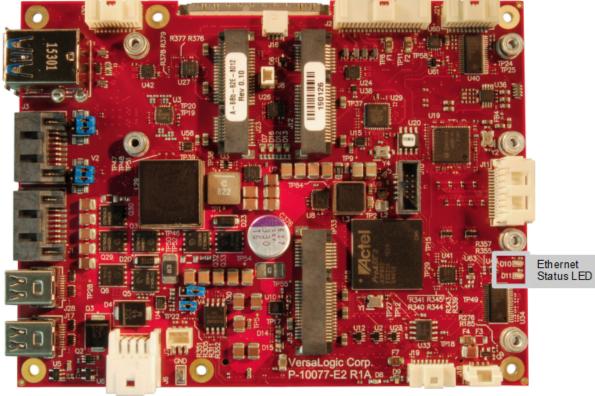

| Figure 5. Top Baseboard Connector Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |

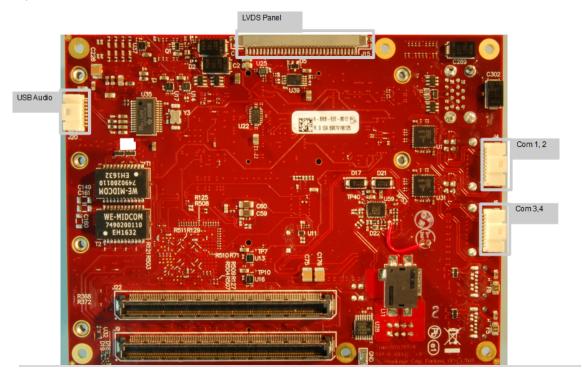

| Figure 6. Bottom Baseboard Connector Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| Figure 7. Main Power Connector Pin Orientation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

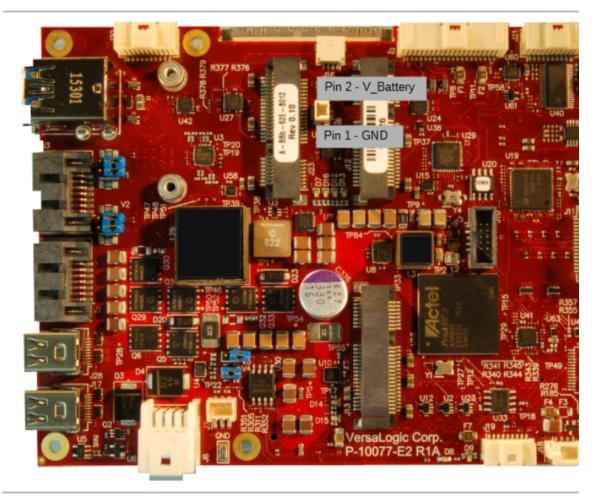

| Figure 8. Location and Pin Orientation of the Battery Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| Figure 9. VL-CBR-0203 Latching Battery Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

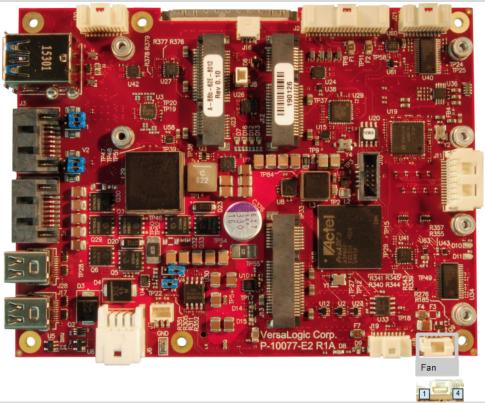

| Figure 10. Location and Pin Orientation of the CPU Fan Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27      |

| Figure 11. Location of Status Indicator LEDs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

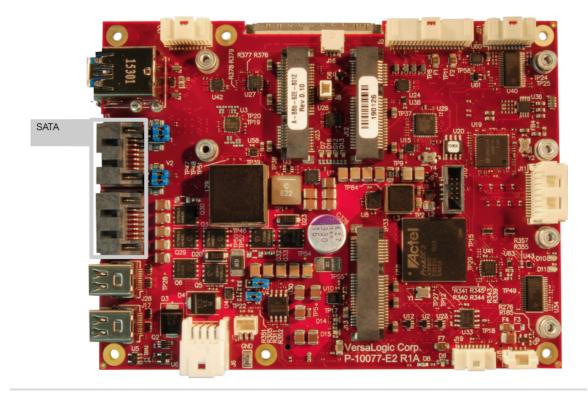

| Figure 12. Location of the SATA Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |

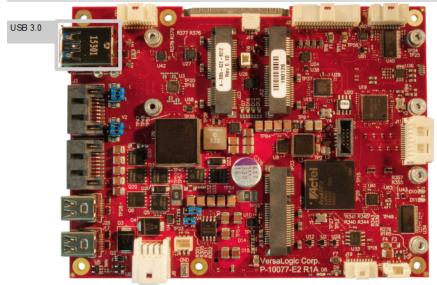

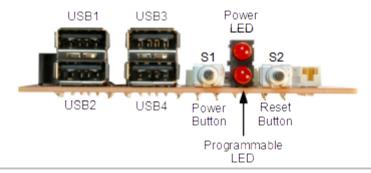

| Figure 13. Location of the USB Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

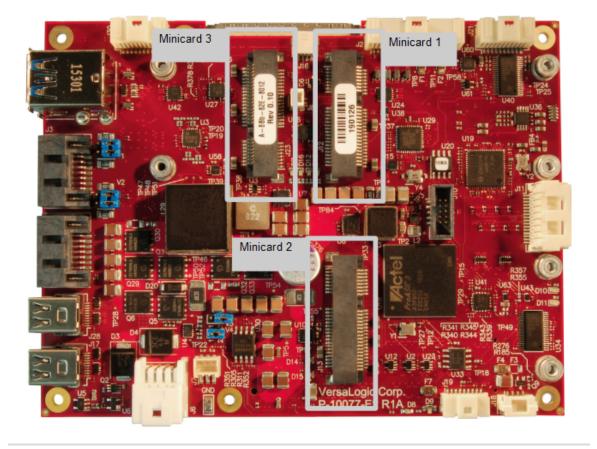

| Figure 14. Location of Mini PCIe Sockets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |

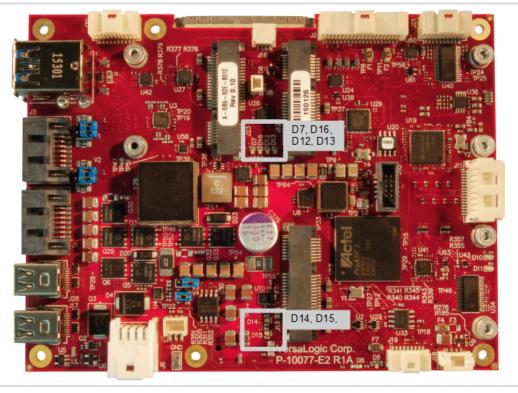

| Figure 15. Mini PCIe Status LEDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

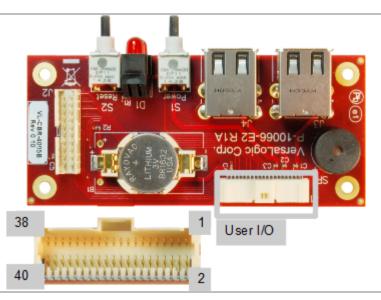

| Figure 16. Location and Pin Orientation of the User I/O Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

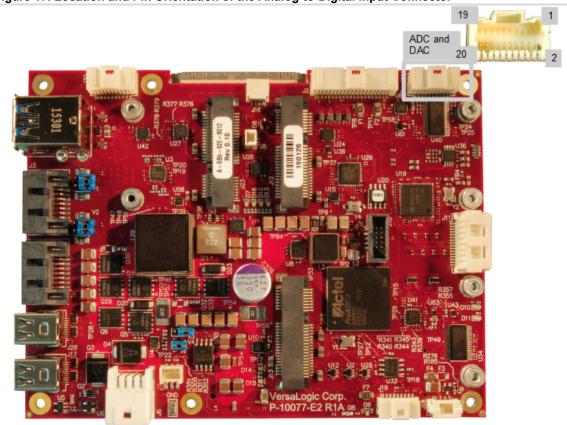

| Figure 17. Location and Pin Orientation of the Analog-to-Digital Input Connector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

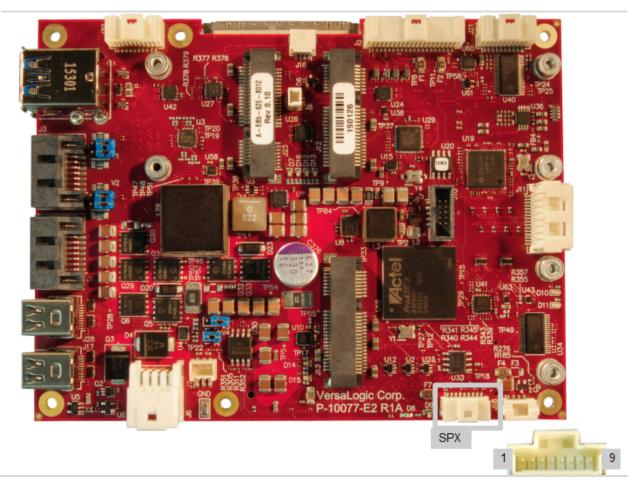

| Figure 18. SPX Connector Location and Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

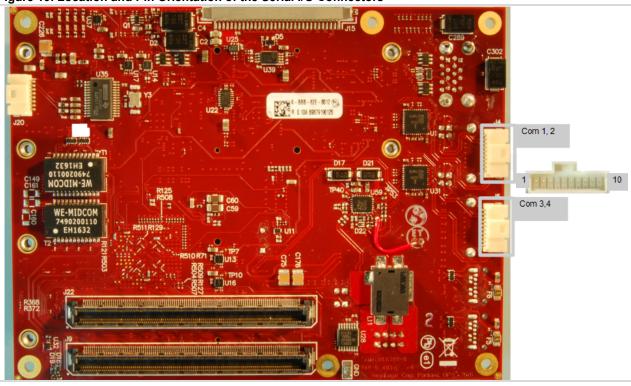

| Figure 19. Location and Pin Orientation of the Serial I/O Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

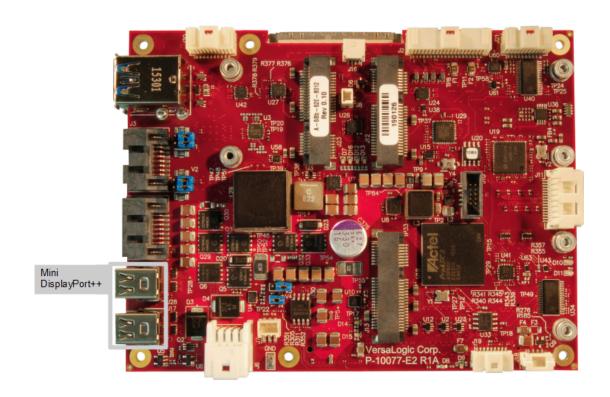

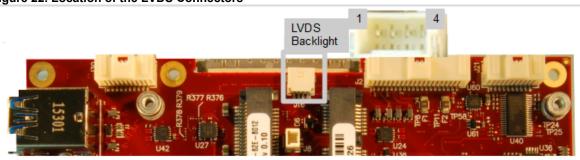

| Figure 20. Location of the Mini DisplayPort++ Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48      |