# **TWR-P1025**

Hardware Getting Started Guide

Rev. 1

## 1 About this Document

This document describes how to connect the TWR-P1025 card and verify its basic operation. It also provides settings for the switch and instructions for connecting peripheral devices. It also includes instructions for connecting the TWR-P1025 to an integrated development environment (IDE), such as Freescale's CodeWarrior. However, instructions for working with the IDE are beyond the scope of this document.

## 1.1 Definitions, Acronyms, and Abbreviations

CPLD Complex Programmable Logic Device

DIP Dual In-line Package

EEPROM Electrically Erasable, Programmable Read Only Memory

GETH Gigabit Ethernet HW Hardware I<sup>2</sup>C (bus) Inter-IC Bus

UART Universal Asynchronous Receiver/Transmitter

## 2 Getting Started

## 2.1 Checking the Switches

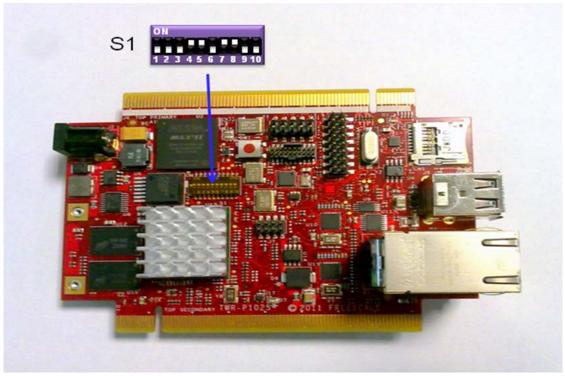

The TWR-P1025 board has one 10-way dual in-line package (DIP) switch. The default DIP switch positions (as shown in Figure 2-1 and described in Table 2-1) provide working set up values for the board. Ensure that the default positions are set, and verify the board is operational before changing the switches.

Figure 2-1: Default Switch Settings

The following Table 2-1 lists default switch settings.

Table 2-1: Default Switch Settings (In RED)

| Feature      | Settings<br>[OFF=1 ON=0]                      | Comments                                                                                                                                 |                            |                              |                      |                 |  |  |

|--------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------|----------------------|-----------------|--|--|

| S1.1         | OFF<br>ON                                     | Reserved                                                                                                                                 |                            |                              |                      |                 |  |  |

| S1.2         | OFF<br>ON                                     | PCIE_HOST_AGENT Selection P1025 is Host P1025 is Agent                                                                                   |                            |                              |                      |                 |  |  |

| S1.3         | OFF<br>ON                                     | Reserved                                                                                                                                 |                            |                              |                      |                 |  |  |

| S1.4         | OFF<br>ON                                     | CFG_CPU0_1_BOOT  Both Cores run after reset  Core0 boots, Core 1 in holdoff after reset                                                  |                            |                              |                      |                 |  |  |

| S1.5         | OFF<br>ON                                     | BOOT_SEQ Boot Sequencer ON Boot Sequencer OFF                                                                                            |                            |                              |                      |                 |  |  |

| S1.6         | OFF<br>ON                                     | LOCALBUS_QE_MUXSEL  Local bus pins muxed with QE function as local bus in CPLD  Local bus pins muxed with QE function as QE pins in CPLD |                            |                              |                      |                 |  |  |

| S1.7<br>S1.8 | CPU_SPEED_SELECT0<br>SW1.7                    |                                                                                                                                          | CPU_SPEED_SELECT1<br>SW1.8 | CORE(0 &1)<br>Speed<br>(MHz) | QE<br>Speed<br>(MHz) | SYSCLK<br>(MHz) |  |  |

|              | ON                                            |                                                                                                                                          | ON                         | 533                          | 266                  | 66.667          |  |  |

|              | NOTE: All other switch settings are reserved. |                                                                                                                                          |                            |                              |                      |                 |  |  |

| S1.9         | OFF<br>ON                                     | ETH_TDM_SEL  Ethernet1 clock routed to P1025 through CPLD  TDM Clock routed to P1025 through CPLD                                        |                            |                              |                      |                 |  |  |

| S1.10        | OFF<br>ON                                     | Reserved                                                                                                                                 |                            |                              |                      |                 |  |  |

## 2.2 Assembly and Connection of the Board

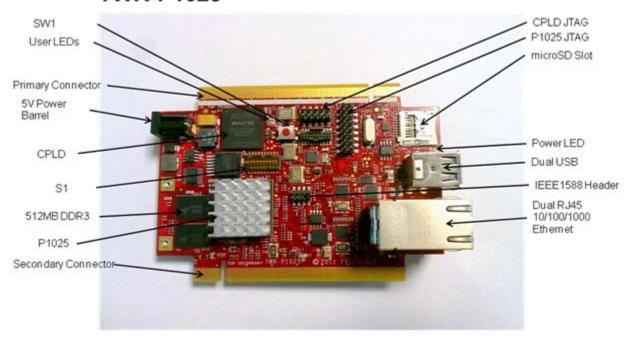

The TWR-P1025 is powered through a barrel connector. This barrel should be supplied by a 5V @5A supply. (Figure 2-2)

#### NOTE

Under normal operating conditions, the heat sink on the P1025 may become hot.

## 2.3 Performing Initial Board Power-Up and Checking the LEDs

- 1. Apply power to the board through the barrel connector.

- 2. Check for completion of the reset sequence indicated by the LEDs (Figure 2-2). Table 2-2 describes the LED operation.

#### 3. When powered up:

- a. The LED D5 will turn on to indicate 3V3 Power is present.

- b. D7 will turn ON then OFF This LED is connected to the P1025 ASLEEP signal.

- c. D2 will blink ON then turn and remain OFF, while D3 will remain ON.

- d. Any Ethernet activity will be indicated by the LEDs on the RJ45 connector

- e. D1 indicates RX or TX activity on the USB UART.

#### NOTE

SW1 performs a full reset of the board (P1025 Hard reset + PHY resets)

**Table 2-2: LED Operation**

| Description     | Ref   | Color        | LED On                                  | LED Off                |

|-----------------|-------|--------------|-----------------------------------------|------------------------|

| UART Activity   | D1    | Orange       | Flash for Activity                      | Off for no<br>Activity |

| CPLD            | D2    | Green        | User Configured via P1025 QE_PB27       |                        |

| CPLD            | D3    | Green        | User Configured via P1025 QE_PB3        |                        |

| 3V3 Power       | D5    | Green        | 3V3 Power ON                            | 3V3 Power<br>OFF       |

| P1025 ASLEEP    | D7    | Green        | P1025 in Reset                          | P1025 exited<br>Reset  |

| Ethernet eTSEC1 | Lup   | Green        | ON - Link<br>Blink - Activity           | No Link                |

| Ethernet eTSEC1 | Rup   | Green/Orange | Orange -<br>1000Mbps<br>Green – 100Mbps | 10Mbps                 |

| Ethernet eTSEC3 | Ldown | Green        | ON – Link<br>Blink - Activity           | No Link                |

| Ethernet eTSEC3 | Rdown | Green/Orange | Orange -<br>1000Mbps<br>Green – 100Mbps | 10Mbps                 |

## 2.4 Connecting the USB UART

The TWR-P1025 comes preloaded with u-boot/linux. Serial connectivity for P1025 is provided through the mini type B USB connector (labeled mini USB UART in Figure 2-3). Note that USB Drivers should be installed onto the host PC before the serial terminal is used. You can download from:

http://www.ftdichip.com/Drivers/VCP.htm (FT2232).

You can set up a serial terminal using PC communication, such as hyper terminal set to 115200 Baud, 8 data bits, no parity, 1 stop bit. Select the first COM port assigned to the USB UART Virtual COM port.

## 2.5 Connecting the JTAG Connectivity Unit to the Board

The JTAG connectivity unit (USB tap) enables the CodeWarrior software to work with the board.

- 1. Connect the JTAG connectivity unit to the P1025 JTAG connector J3. Pin 1 is marked on the board.

- 2. Switch on power to the board.

- 3. Check for completion of the reset sequence.

- 4. Continue as per standard CodeWarrior instructions.

## 2.6 Setting the Board for User-Specific Development

Main headers/connectors are as follows (Figure 2-2 and Figure 2-3)

- J3 P1025 JTAG/COP

- J1 CPLD JTAG

- J4 QE UART Expansion

- J7 IEEE1588 Header

- Primary and Secondary Elevators

- o LCD Local Bus

- O QE UART for RS485 or RS232 (UCC3 and UCC7)

- O 10/100 Mbps Ethernet (UCC1 and UCC5)

- o GPIO

- o SerDes (PCIe, SGMII)

- o SPI

- o I<sup>2</sup>C

## TWR-P1025

Figure 2-2: Primary Side Main Features

Figure 2-3: Secondary Side Main Features

## **Support**

Visit freescale.com/support for a list of phone numbers within your region.

## Warranty

One (1) year limited warranty. Visit us at freescale.com/warranty for complete warranty information.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc. CodeWarrior is a trademark or registered trademark of Freescale Semiconductor, Inc. in the United States and/or other countries. All other product or service names are the property of their respective owners.

Copyright © 2012 Freescale Semiconductor, Inc. All rights reserved.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.